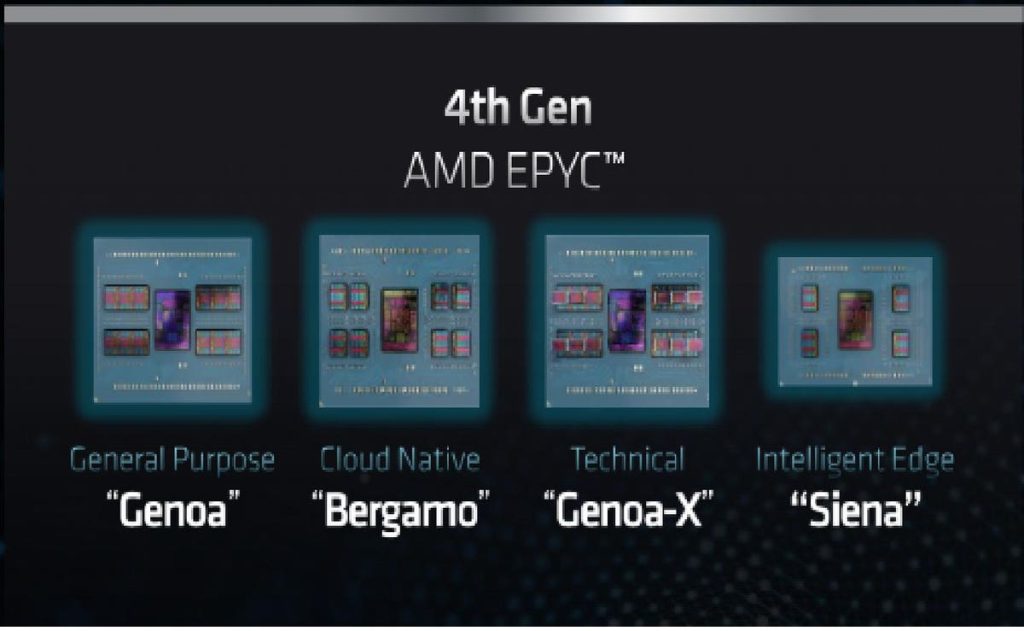

Workload optimized computing has been Advanced Micro Devices’ (NASDAQ: AMD) story since they first launched the 4th generation Epyc family of processors with Genoa in November of 2022. Since then, they’ve delivered on their promises by launching Genoa-X, Bergamo and now completing the story arc with the launch of Siena. Genoa is the general-purpose foundation of the family, Genoa-X specifically targets technical computing, Bergamo targets cloud-native computing and now with the Siena launch, the Epyc family is targeting cloud services, intelligent edge and telco deployments. What modifications on the Epyc architecture did AMD employ for these latest workloads but also, how did AMD essentially launch four product lines in less than 12 months?

Epyc 8004 Series: Code Named Siena

According to AMD, in targeting cloud services, intelligent edge applications and telco deployments, the primary design driver for the newest Epyc family member was placing and securing data, compute and storage closer to points of creation and consumption (e.g. the edge) as required by pervasive intelligence to unlock new experiences and services. At the edge, datacenters face limited availability of power and space as they are often deployed in challenging physical locations, such as at base station sites, at offices and campuses, or in areas where acoustic noise from server cooling is an important consideration, such as at retail branch locations, in offices or near medical equipment. Consequently, when compared with Genoa, Siena was optimized for total cost of operation (TCO) and power efficiency while still providing the performance and cache per core needed for those types of workloads.

To achieve this, AMD replaced the Zen4 core used in the Genoa CPU with the Zen4c core in Siena to reduce the power per core, increase core density and lower system power while still maintaining logical equivalency with the same instruction set, software, and L1 and L2 cache architectures. Siena is also available with up to 96 lanes of PCIe Gen5 input/output (I/O) to support expansion as well as an optimized memory and storage architecture supporting 6 channels and up to 1.152TB of DDR5 memory and 48 lanes of CXL 1.1+. Siena is offered in configuration with up to 64 cores and power envelopes down to 70W.

Siena Ecosystem Adoption

Along with the launch of the processor, AMD also announced three OEM partner offerings and solutions that are taking advantage of Siena’s capabilities. Dell Technologies released the Dell PowerEdge C6615 server “to maximize compute performance in air-cooled environments without having to alter power or cooling capabilities” according to Travis Vigil, Senior Vice President of Product Management for Dell. Lenovo announced its latest ThinkEdge SE455 V3 targeted at enabling next generation artificial intelligence applications at the edge in an energy efficient platform while allowing for high performance, storage and expandability. While not releasing a specific product, Ericsson is considering Siena for Cloud RAN computation acceleration solutions in high-traffic mobile networks that also require best-in-class performance and energy efficiency.

Chiplets are the Key

Modifying the primary core as well as optimizing I/O and memory and storage are big enough changes to typically require a separate product design cycle of at least 12 months or more for each variant. Not only did AMD achieve this feat for this launch, but the company accomplished this task within that same 12-month time frame (actually slightly less at 10 months), while also introducing modifications to the original Genoa chip for Genoa-X and Bergamo. How did they do it?

The answer is: the company used chiplets. From the beginning of this latest generation of Epyc processors, AMD decided to use chiplets to allow for changes to critical architectural components such as the primary compute core, I/O, memory and storage. This foresight has borne fruit for AMD and has allowed them to make modifications quickly while minimizing technical and manufacturing risks typically associated with these types of changes. While this may be the last of the announced Zen 4/4c roadmap, Tirias Research believes that we will continue to see more workload specific modifications from AMD in the future that leverage different chiplet configurations that are optimized for a variety of use cases.

Tirias Research tracks and consults for companies throughout the electronics ecosystem from semiconductors to systems and sensors to the cloud. Members of the Tirias Research team have consulted for AMD, IBM, Intel, MediaTek, Nvidia, Qualcomm and with other companies throughout the Embedded, Mobile, PC, AI, and Computing ecosystems.

Read the full article here